to the contents of register 2, R2. By changing the value

in R1, different operands may be addressed. This is

particularly useful for addressing memory locations in

arrays. Indexing is a very useful troubleshooting tool.

A short routine can be written to form a program loop

to isolate on a specific malfunction.

On some computers, a CPU register is dedicated to

this indexing function. In those cases, it is called an

index register and is usually 3-bits or more depending

on the computer type.

Some computers permit a

general-purpose register to be used as an index register.

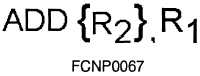

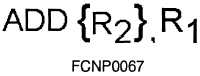

Indirect Operand Addressing

Indirect addressing enables the operand address to

vary during program execution by specifying a location

in memory or a register in the instruction that tells where

the address will be stored. See figure 8-15. In this

example, the braces are used to tell that register 2 has

been specified to hold the operand address. This means

the contents of the main memory location whose

address is contained in R2 are added to the contents of

R1. Like the indexed mode of addressing, the indirect

mode of addressing offers flexibility and is useful in

addressing an array of data. Because the actual address

pointing to an array can be stored separately from the

program in memory, a large number of array pointers

can be used.

Relative Operand Addressing

In many computers, particularly those with

multiprogramming capabilities, a separate set of

registers called base registers is used to define the start

of particular blocks or segments of memory. Each

block of memory could contain a separate application

program. The contents of a base register is called the

base address.

Any execution of instructions or

referencing of operands within the block of memory

defined by the base requires that an offset or relative

address be used. The offset is added to the base during

instruction execution to allow reference of the correct

instruction or operand address.

INSTRUCTION SIZE

Each address of memory (main or ROM) contains

a fixed number of binary positions or bits. The number

Figure 8-15.—Example of indirect addressing.

of bits stored at a single address varies among types and

generations of computers. For example, some store 8

bits (1 byte) at each location; others store 16, 32, or more

bits at each location. The size of each memory location

or memory word has a direct effect on the execution of

machine instructions.

Basic instructions deal with full word exchanges

as the register size is usually the same as the memory

word size. In most computers, particularly those with

large memory words, the capability exists to transfer

less than a full memory word of information between

memory and the applicable register.

This allows

memory words and registers to be further divided into

economically sired bit groups for the most efficient use

of memory for information storage and handling. For

example, it is preferable to store two 8-bit characters in

one 16-bit memory location than to waste an extra

16-bit location for the second character. Let’s examine

some of the various instruction sizes.

Full- or Single-Word Instructions

A full- or single-word instruction simply uses all

the data contained in the instruction word to execute the

instruction regardless of the size: 8-bit, 16-bit, and so

on. Refer back to figures 8-3 and 8-5 for examples of

full- or single-word instructions, 16-bit and 32-bit.

Half-Word Instructions

Half-word (upper or lower half) instructions consist

of one-half of the normal instruction word size. The

half-word instructions are executed by acquiring the

complete normal instruction word, consisting of the

half-word instruction to be executed and the next

sequential instruction.

After the first half-word

instruction is executed, it is followed by the execution

of the next sequential half-word instruction. If only one

half-word instruction is used, it is usually located in the

upper half of the instruction word with all zeros in the

lower half of the instruction word. Refer back to figures

8-6 and 8-7 for examples of a half-word instruction.

Character-Addressable Instructions

In computers with word lengths greater than 8 bits,

character-addressable instructions allow specified bit

fields (called characters) of a word to be processed by

the instruction. This is done in lieu of processing a

whole-, half-, or quarter-word operand. Character

addressing is permitted only when the instruction is

executed in the indirect address mode. The particular

operand bit field to be acquired is specified by the

8-12