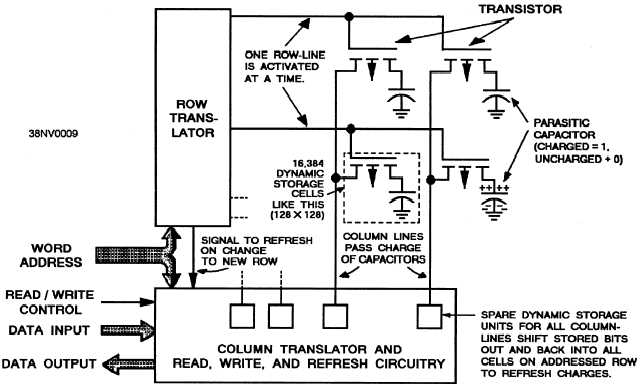

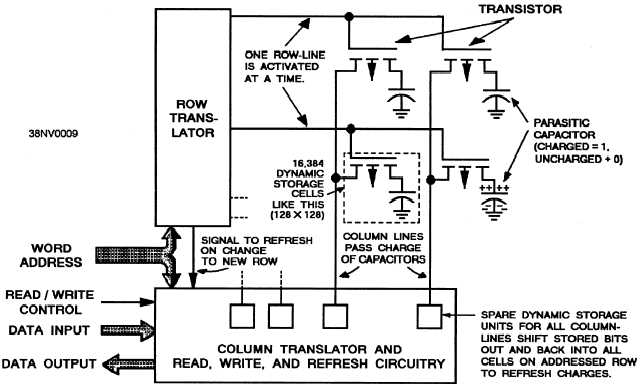

Figure 6-32.—DRAM storage cell.

column lines using switching circuitry in the column

selector section. A read/write control tells memory

whether to read or write.

The dynamic RAM cell is less complex than a static

cell because it does not use a latch to store data. A

parasitic capacitors formed in the integrated circuit and

this becomes the storage element, as pictured in figure

6-32. The single transistor switch is used to isolate or

select one particular cell from the entire memory array.

Because the basic dynamic cell design is simple and

contains few elements, it is possible to achieve much

higher densities than with static cell designs.

A typical memory system may be formed from

many 16K word dynamic RAM parts. These parts are

usually structured as 16K by 1, or 16,384 words of only

one bit each. Larger memory words are made by

ganging as many chips as required. This allows greater

flexibility for system designers to organize memory

systems with a small or wide data bus (for example,

16K by 8, 16K by 16, or 16K by 32). Circuit boards

that are extremely cost-effective for large mainframes

are easily created with densely packed dynamic RAM

parts.

Power consumption by dynamic RAM is another

advantage over static RAM. Because the dynamic

RAM cell does not use a latched design to hold data as

do the static RAM parts, the power consumed by each

cell is negligible when it is not being accessed. Most of

the power consumed occurs during a read or write

operation and a small amount is consumed during the

refresh cycle.

The lower power consumption of

dynamic RAM leads to lower cooling requirements and

smaller power supplies because of the reduced memory

power needs.

One disadvantage that a dynamic RAM has is the

need to refresh the entire memory array within a certain

period of time (usually two milliseconds). The DRAM

memory cells do not retain their charged state for more

than a few milliseconds. DRAM cells are subject to

degradation due primarily to time and temperature. To

retain information, the content of each memory cell

must be refreshed before the charge dissipates. The

memory array may be refreshed in one of two ways:

externally or internally. Externally is more cost

effective because a single refresh address generator is

shared by the entire memory array. A type of DRAM,

time volatile memory (TVM) uses a battery backup to

maintain refresh for 30 minutes after the computer has

been powered down or power has been lost.

In our explanation of dynamic RAM organization

and operation, we use two examples to discuss the

architecture, address selection, and read/write/refresh

6-25