optimizing the CPU’s time, so the CPU is not involved

in all transactions, including the I/O instructions. We

cover those methods later in this topic. However, for

computers that have an IOC, the IOC is a processor in

its own right.

We focus our discussion of I/O

instructions on I/O processors with an IOC. An IOC is

capable of executing its own set of instructions

specifically designed to govern I/O operations for those

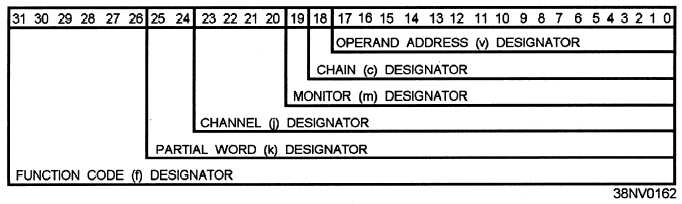

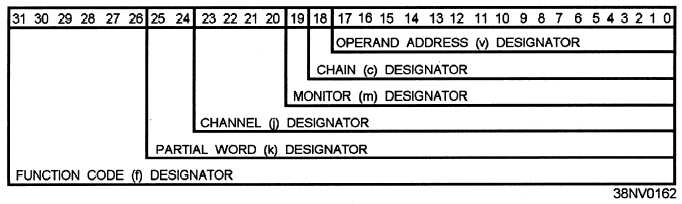

channels/ports handled by the particular IOC. Figure

7-10 shows the format of an example IOC instruction.

This format is used for some mainframes and some

minis. The designators shown are for a typical I/O

instruction and may vary with IOC instructions. Each

IOC executes instructions stored in main memory in the

same manner as the CPU executes instructions. There

are two basic types of IOC instructions: command

instructions and chaining instructions.

Command instructions are executed by the IOC

under the control of the CPU’s main program. Chaining

instructions are executed under the command of an

active channel (I/O operation in progress) chain. Some

IOC instructions peform the same functions whether it

is a command or a chaining instruction.

Command Instructions

Command instructions provide control over IOC

single or dual channel operations. They are executed

individually using the following process. The CPU

executes an I/O command start instruction, which is

a CPU instruction. The I/O command start instruction

specifies or addresses an IOC(s) and then halts further

CPU processing. The addressed IOC then references

specific main memory addresses (the command cell)

and executes the IOC command instruction previously

stored in the addresses. At completion of the instruction

execution, the IOC will clear assigned bits of the

command cells to indicate to the CPU that the command

has been processed and to release the CPU to continue

further processing. This is one instance in interrupt

driven I/O operations where the CPU will delay

processing while waiting for an I/O operation to take

place.

The instruction contained in the command cell will

cause the IOC to perform a variety of channel activity

functions. The most common operations deal with

initiating a new chain or terminating a chain in progress.

Other commands are used to master clear individual

channels, enable or disable a variety of interrupts,

monitor channel status, load or store control memory,

and initiate the IOC built-in test (BIT).

Chaining Instructions

Chains of IOC instructions are stored in memory by

the main CPU program before the I/O operation takes

place. The actual execution of chaining instructions is

independent of the CPU. Only a command instruction

execution from the command cell will delay CPU

processing.

There can be an input chain and/or an

output chain being executed for each channel. Input or

output chains deal primarily with the transfer of blocks

of information.

A chain consists of IOC control words, command

words, output data words, and specified locations for

Figure 7-10.—IOC instruction format.

7-10